作为数字集成电路的主流逻辑形式,互补金属氧化物半导体(CMOS)逻辑架构为硅集成电路技术的发展和繁荣做出了重要贡献。CMOS逻辑门包含一个由空穴型场效应晶体管(p-FET)组成的上拉网络和一个由电子型晶体管(n-FET)组成的互补下拉网络。与其他类型的逻辑类型相比,CMOS电路具有高噪声容限和低功耗优势,因而被广泛的应用于数字集成电路中。近来,研究人员试图采用具有更高迁移率的半导体来构建新型晶体管,从而推进未来集成电路的发展。然而,比硅更高的载流子迁移率的半导体材料(例如砷化铟、锗、碳纳米管等)通常具有更小的带隙,其场效应晶体管会遭受严重的栅致漏极漏电流效应,致使CMOS逻辑门容易出现漏电流高、电压损耗大等现象,严重阻碍了这些半导体在超大规模集成电路中的应用。因此,有必要针对性的开发出一种新的逻辑形式,以推动高性能、高噪声容限和低功耗的窄带隙半导体集成电路发展。

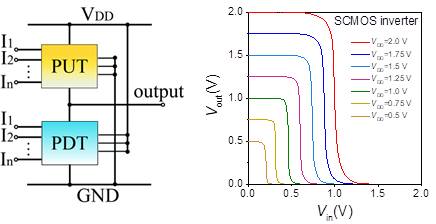

针对以上问题,北京大学信息科学技术学院电子学系碳基电子学研究中心、纳米器件物理与化学教育部重点实验室的张志勇-彭练矛联合课题组提出了一种新集成电路方案,即采用强反馈互补金属氧化物半导体(Strengthened CMOS, SCMOS)逻辑形式和相应的改进晶体管,在不增加电源数目的情况下,能够有效抑制窄带隙半导体集成电路中的漏电流和逻辑损耗。课题组以碳纳米管器件作为例子,演示了具有低功耗和严格轨对轨输出的SCMOS电路。所有的碳纳米管晶体管都被设计成双栅结构:主栅G1和控制栅G2,在集成电路中将所有上拉晶体管(p-FET)的G2连接到地,将所有下拉晶体管(n-FET)的G2连接到电源,如此连接的G2钳制了器件关态时的靠近漏端的沟道电势,有效抑制了GIDL效应,并且极大降低了开态时的串联电阻。因此,SCMOS架构不仅降低了窄带隙而导致的电流泄漏,而且保持了高迁移率半导体晶体管的高性能。课题组还基于SCMOS架构实现了一些典型的数字逻辑门,包括反相器、与非门、或非门、多级门反相器串和环形振荡器,测试结果表明,与CMOS逻辑门相比,SCMOS逻辑门具有严格的轨对轨输出,静态功耗降低了三个数量级,并且与CMOS集成电路具有类似甚至更高的工作速度。更为重要的是,SCMOS逻辑架构可以推广到任何窄带隙半导体的集成电路中,以同时提供高性能和低功耗。

2020年10月30日,相关研究成果以“基于窄带隙半导体的高性能、低功耗电路应用的强反馈互补金属氧化物半导体逻辑(Strengthened Complementary Metal-Oxide-Semiconductor Logic for Small Band-Gap Semiconductor Based High-Performance and Low-Power Application)”为题,在线发表于材料领域著名期刊《美国化学学会.纳米》(ACS Nano);北京大学电子学系博士研究生赵晨怡、仲东来为共同第一作者,张志勇、彭练矛为共同通讯作者。相关课题得到国家重点研发计划、北京市科技计划等资助。

论文链接:https://pubs.acs.org/doi/10.1021/acsnano.0c05554