集成电路的发展要求互补金属氧化物半导体(CMOS)晶体管在持续缩减尺寸的同时提升性能,降低功耗。随着主流CMOS集成电路缩减到亚10 nm技术节点,采用新结构或新材料对抗场效应晶体管中的短沟道效应、进一步提升器件能量利用效率变得愈加重要。在诸多新型半导体材料中,半导体碳纳米管具有超高的电子和空穴迁移率、原子尺度的厚度和稳定的结构,是构建高性能CMOS器件的理想沟道材料。已公开的理论计算和实验结果均表明,碳管CMOS晶体管采用平面结构即可缩减到5 nm栅长,且较同等栅长的硅基CMOS器件具有10倍的本征性能-功耗综合优势。

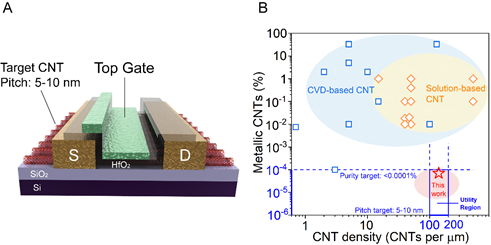

碳纳米管集成电路批量化制备的前提是实现超高半导体纯度(>99.9999%)、顺排、高密度(100~200 /μm)、大面积均匀的碳纳米管阵列薄膜(见图一)。长期以来,材料问题的制约导致碳管晶体管和集成电路的实际性能远低于理论预期,甚至落后于相同节点的硅基技术至少一个数量级,因而成为碳管电子学领域所面临的最大的技术挑战。

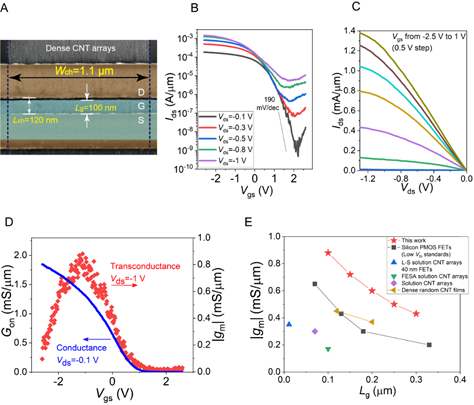

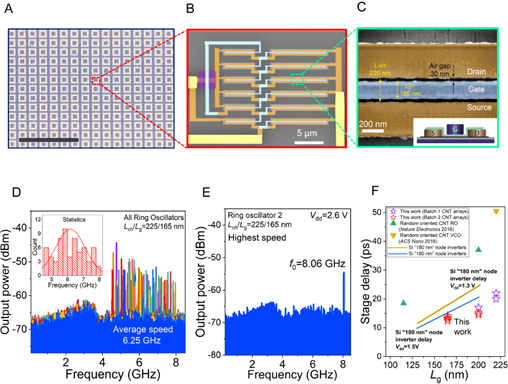

北京大学信息科学技术学院电子学系/北京大学碳基电子学研究中心、纳米器件物理与化学教育部重点实验室张志勇教授-彭练矛教授课题组发展全新的提纯和自组装方法,制备高密度高纯半导体阵列碳纳米管材料,并在此基础上首次实现了性能超越同等栅长硅基CMOS技术的晶体管和电路,展现出碳管电子学的优势。该课题组采用多次聚合物分散和提纯技术得到超高纯度碳管溶液,并结合维度限制自排列法,在4英寸基底上制备出密度为120 /μm、半导体纯度高达99.99995%、直径分布在1.45±0.23 nm的碳管阵列(见图二),从而达到超大规模碳管集成电路的需求。基于这种材料,批量制备出场效应晶体管和环形振荡器电路,100 nm栅长碳管晶体管的峰值跨导和饱和电流分别达到0.9 mS/μm和1.3 mA/μm(VDD=1 V,见图3),室温下亚阈值摆幅为90 mV/DEC;批量制备出五阶环形振荡器电路,成品率超过50%,最高振荡频率8.06 GHz远超已发表的基于纳米材料的电路(见图4),且超越相似尺寸的硅基CMOS器件和电路。

该项工作突破了长期以来阻碍碳管电子学发展的瓶颈,首次在实验上显示出碳管器件和集成电路较传统技术的性能优势,为推进碳基集成电路的实用化发展奠定了基础。2020年5月22日,相关研究成果以《用于高性能电子学的高密度半导体碳纳米管平行阵列》(Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics)为题,在线发表于《科学》(Science,第368卷6493期850~856页);电子学系2015级博士研究生刘力俊和北京元芯碳基集成电路研究院工程师韩杰为并列第一作者,张志勇和彭练矛为共同通讯作者。

上述研究得到国家重点研发计划“纳米科技”重点专项、北京市科技计划、国家自然科学基金等资助。湘潭大学湖南省先进传感与信息技术创新研究院、浙江大学、北京大学纳光电子前沿科学中心等单位研究人员参与合作。

原文链接:https://science.sciencemag.org/content/368/6493/850

图一 大规模集成电路对碳管材料的要求

图二 高密度、高纯度半导体碳管阵列的制备和表征

图三 高性能碳管晶体管

图四 碳管高速集成电路